Chipletz是由來自Advanced Micro Devices, Inc. (AMD)和其他主要系統供應商的業界資深人士出資成立的一家新創公司。他們的願景是透過開發先進的封裝技術,將半導體封裝內的功能徹底革新,以填補摩爾定律發展速度放緩與運算效能需求不斷增加這兩者間的差距。Chipletz的Smart Substrate產品可幫助以異質方式將多個IC整合到一個封裝中,以支援關鍵AI工作負載、沉浸式消費者體驗和高效能運算。

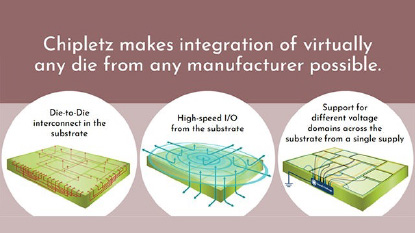

Chipletz技術專精的工程師團隊在半導體設計、製造和封裝方面擁有數十年經驗,能滿足此一需求。Chipletz正在將系統級封裝概念推向未來,為未來數年的額外效能提升開闢一條前進之路,同時讓半導體整合的經濟模式重新洗牌。Chipletz以Smart Substrate為基礎的獨特平台,讓幾乎任何製造商的任何晶粒都能整合在一起。

Smart Substrate提供晶粒至晶粒互連及高速I/O,並支援從單一電源提供不同的電壓域,勝過現有的多晶片模組和系統級封裝選擇。

圖說:(左)Chipletz 技術長 Michael Su與 Chipletz執行長 Bryan Black。

Chipletz技術長Michael Su提到,基於我們的Smart Substrate進行設計對設計師及其設計工具提出了許多具有挑戰性的要求。在評估EDA供應商和他們的技術時,這些要求是我們評估的重點依據。

為了評估Siemens Xpedition™半導體封裝技術,Chipletz使用一個巨型SoC設計,兩側搭配四個HBM堆疊,並在Smart Substrate中整合去耦電容器。元件尺寸約為50 mm x 65 mm,總共8000多個net使用大約120萬個過孔連接晶粒,並在一個含有2800個錫球的BGA上使用超過18萬個元件腳位。此設計使用Smart Substrate技術打造而成,並利用150多個重複使用電路,使得金屬層減到只有9層,而前一版使用的矽中介層需要16層金屬。

圖說:Chipletz Smart Substrate

Chipletz透過許多使用案例情境對Siemens的技術和技術專家執行了廣泛的評估,以確認解決方案是否適合未來的多晶粒異質設計。作為此次評估的結果,Chipletz選用了Siemens的半導體封裝技術,設計以Smart Substrate為基礎的獨特先進封裝。

Chipletz執行長Bryan Black表示:「作為無晶圓基板廠商和小晶片整合商,我們開發出先進的封裝技術,以填補摩爾定律發展速度放緩與運算效能需求不斷增加這兩者間的差距。選擇Siemens是因為他們展現了卓越的技術能力,並在先進異質半導體封裝設計方面擁有豐富的專業知識。」

自從選擇Siemens後,該團隊按計劃完成了第一個設計,並對他們在合作夥伴、供應商和技術方面做出的正確選擇繼續感到滿意。

Chipletz預期他們接下來將著重於熱與熱致機械應力領域,Siemens在這兩個領域以成熟的技術領先群倫。

Chipletz成立於2021年,是一家無晶圓基板廠商,致力開發先進封裝技術,以填補摩爾定律發展速度放緩與運算效能需求不斷增加兩者間之間的差距。該公司的Smart Substrate產品可幫助將多個IC整合到一個封裝中,以支援關鍵AI工作負載、沉浸式消費者體驗和高效能運算。

Chipletz計劃在2024年初為客戶及合作夥伴交付自家初始產品。

將通常會實作成單一同質系統單晶片 (SoC) ASIC 元件之物,分拆成未封裝的離散式 ASIC 元件(也稱為小晶片)。這些小晶片通常提供特定功能實作在最佳晶片製程節點上。使用高速/高頻寬介面將幾個這類小晶片元件安裝並互連到一個封裝,就能以更低的成本提供單體解決方案或實現更高的效能,同時提高良率並降低功耗,而面積僅比異質整合式先進封裝略大一點點。