從降低電壓、智慧動態調整改善晶片功耗問題

- DIGITIMES企畫

晶片功耗問題,已成為現代行動裝置、3C產品最重要課題,因為晶片功耗若無法控制在一定程度,終端產品為了延長電池工作時數,勢必需要追加電池容量,甚至過高的晶片功耗也會造成設計方案還須追加主動散熱設計,如此環環相扣造成產品在體積、耗能、效能各方面都趨於劣勢,降低了終端產品的市場競爭優勢...

一般進行IC晶片設計時,大多會先以功能性考量為主,但若要因應市場競爭,除了功能要求外,晶片本身的功耗表現,已經成為解決方案在市場競爭的重要指標,因為晶片的功耗表現不只影響整體配套設計的複雜度,甚至也會成為左右終端產品的市場競爭力指標。

以行動終端產品為例,若採行的晶片解決方案在功耗表現方面設計不佳,就會造成電池的效能低下,導致產品電池續航能力出現明顯劣勢!而設計方案中若為了提高整體效能,高功耗也會連帶使設計方案的散熱需求變得更高,不只機殼需要考量設置更多散熱孔位,甚至還需在設計方案追加主動散熱機制,例如更大的散熱片或是散熱風扇,自然造成終端設計產品的尺寸不易微縮,或是使產品出現高熱的設計劣勢。

善用低功耗元件與新材料 打造省電行動設備

如果在設計方案中導入低功耗晶片元件,可在有限電池容量下達成設計方案要求的電池效能設定,晶片的運作溫度也不會飆升太多,自然就能減少散熱片元件成本,讓BOM料件成本得到最直接的精省,令產品的成本結構更具競爭力。

降低晶片的功耗,還可以從改用更低耗能的材料、增加智慧耗能調節、降低晶片工作電壓等多種方案,來降低晶片設計方案的功耗。

通常,使用新的低功耗材料,是降低晶片功耗的最快捷徑,但新材料的設計門檻相當高,一方面不光是電學的問題,而是將設計層次拉高到材料科學的問題,通常這對一般無晶圓廠的設計公司是較難掌控的部份,投入成本相對較高,但對功耗改善表現卻是相當顯著。

即便改善材料是最有效降低功耗問題的方案,但面對高成本的實驗與材料技術奧援,在一般元件設計方面並不容易達成, 尤其是採行高效電子遷移的材料,可直接降低晶片本身的功耗問題。例如,若在標準化的CMOS產品加入磁性材料奈米材料,或是新穎的石墨烯改善料件本身的特性,也是相當常見的功耗改善作法。若在此功耗改善方案中,業者必須具前端的材料科學技術能力,同時也必須有豐沛的元件製造經驗,才能掌握透過材料改善元件的功耗問題的技術能力。

像是CMOS產品中的低功耗設計,常會以InGaAs(砷化銦鎵)材料,來進行功耗表現改善,像是Intel在CMOS設計中就嘗試以此設計方向,來降低晶片的工作電壓,透過驅動電壓的調降,進一步改善整體晶片的功耗表現。另一方面,使用石墨烯或在晶片材料添加奈米技術材料的方式,也是未來超低功耗元件的重點設計方案,目前TI已著手進行相關設計開發工作,期待在新設計中創造超低功耗晶片的應用基礎,透過降低材料的電阻值,讓整體晶片的功耗問題可以獲得大幅改善。

透過智慧耗能調節達成節能要求

除了材料外,改善能耗更務實的作法,則是在晶片設計時即考量節能機制,例如透過不同層次的睡眠設計,讓晶片的耗能單位設計,可以在不同深淺程度的睡眠模式獲得彈性調整的空間,達到進階節能的目的。

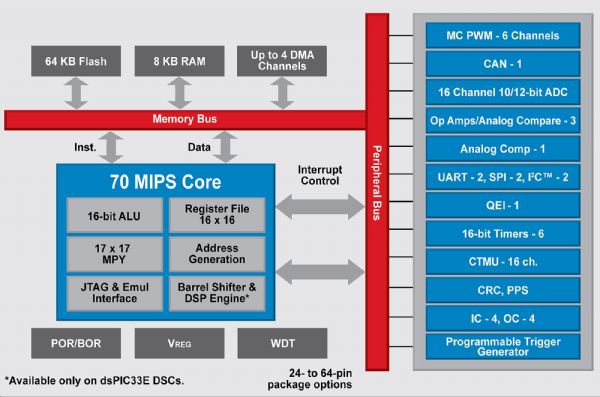

一般的設計方案中,通常驅動電壓越低、驅動的時脈越低,也會讓整體晶片的功耗獲得壓低的成效,但付出的代價可能就是犧牲運作效能!這種透過局部功能性的關閉、或是晶片整體因應不同睡眠機制的功耗控制設計,在簡單的晶片設計中效果較不顯著,反而是在高度集成的SoC(系統單晶片)、CPU與MCU元件上,透過區域節能與電壓、時脈動態調校設計達到的節能效益,可以達到較高的節能效益。

像是Intel在最新的中央處理器中,就設置了Turbo模式,即在正常模式下維持標準運行狀態,避免系統持續維持在高時脈的條件下運作,但當用戶需要高效能的處理資料需求時,即可透過系統熱鍵啟動中央處理器的Turbo功能,此時驅動電壓、時脈可適時提高,讓晶片獲得更高的驅動電壓,提升頻率榨出更多處理效能,也就是利用電池效能去交換處理器效能的折衷設計方案。

節能機制的另一種實踐方案,就是採用SoC設計架構。SoC本身是將多種功能目的晶片整合為一的單晶片產品,結構為內部連結多晶片的單一封裝設計,如果在設計這類SoC晶片時,即將電源管理的需求一併考量,即可在各個功能晶片連接設計中,追加如控制單元晶片開關的dark silicon設計概念,在未使用該項功能晶片時透過省電控制機制令該單元不驅動、不運行,即可達到更具效率的省電效用。此設計方案在行動運算應用的整合處理器設計方案中尤其常見,像是多核心設計的嵌入式SoC,即能因應行動裝置的運行狀態,動態控制驅動核心數量與重點功能的開啟與關閉,達到進階節能的設計目的。

利用降低驅動電壓達到晶片更直接的節能功效

前述透過材料的調整,雖然也能達到降低驅動電壓的效用,但此處談到的降低電壓,反而是因為採行更微縮的線路製程,因為晶片內晶體的連接距離變得更微縮、晶片距離更短,因此晶片可使用更低驅動電壓達到相同的導通或運行效果,像是工作電壓自1.5V上下的晶片,經過新一代的製程設計後,驅動電壓即可降至1.35V亦能穩定運作,光是節省的0.15V水準,就能替原晶片達到60%以上的節能功效。

但透過製程微縮改善功耗的手法,近年也逐漸出現技術瓶頸,因為持續微縮的製程技術,目前已達接近極致的狀態,目前最新方案需要以3D製程或是更先進的微縮設計概念,才能獲得更進階的功耗改善效益。

而利用3D製程的概念,主要源自縮短內部晶體傳輸距離的概念,將內部Inter connect的距離進一步縮短,此即可減少IC內部傳輸功耗,進而降低IC本身的功耗。一般來說,縮短連線距離的方案是追加晶片內的金屬層,而在晶片內的互連層設計中,新方案是利用3D矽晶穿孔(TSV)技術進行設計,但實際上TSV設計方案在製程耗費的成本相當高,省電功效對應晶片製作成本的效益換算,卻未必划算。