英特爾發布最大容量全新Stratix 10 GX 10M FPGA

- 台北訊

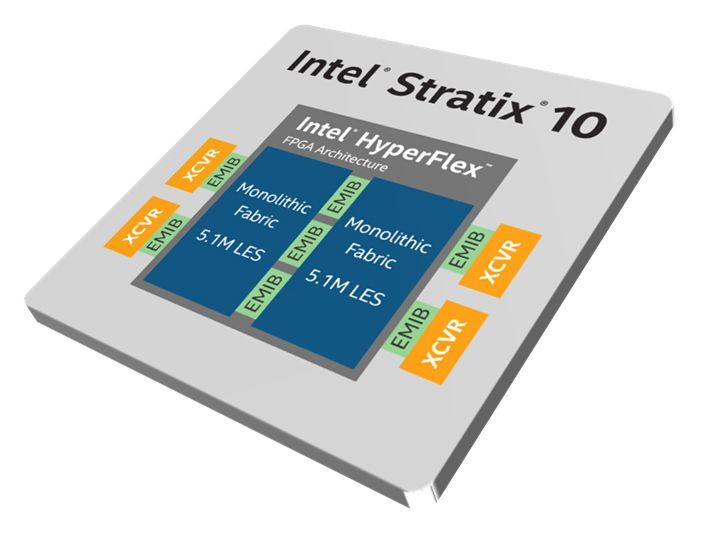

多家客戶現已收到全新Intel Stratix 10 GX 10M FPGA樣品,該產品是全球密度最高的FPGA,擁有1,020萬個邏輯單元,該裝置現已量產。這款元件密度極高的FPGA,是以現有的Intel Stratix 10 FPGA 架構以及英特爾先進的嵌入式多晶片互連橋接(EMIB)技術為基礎所設計。

最新Intel Stratix 10GX 10M FPGA運用EMIB技術融合兩個高密度Intel Stratix 10 GX FPGA核心邏輯晶片(每個晶片容量為510萬個邏輯單元)以及相應的I/O單元。Intel Stratix 10 GX 10M FPGA密度約為Stratix 10 GX 1SG280 FPGA的3.7倍,後者為原Intel Stratix 10系列中元件密度最高的裝置。

ASIC原型設計和模擬市場對當前最大容量的FPGA需求格外殷切,有數家供應商提供商用現成(COTS)的ASIC原型設計和模擬系統。此外,包括英特爾在內的多家大型半導體公司都開發自家的客製化原型設計和模擬系統,並在設計定案(tape-out)前使用該系統來驗證其最大規模、最複雜、風險也最高的ASSP和系統單晶片(SoC)設計。

ASIC模擬和原型設計系統可以幫助設計團隊大幅降低設計風險。因此,包括Intel Stratix 10 FPGA和更早的Stratix III、Stratix IV和 Stratix V裝置在內的Intel FPGA在過去十多年來一直被用為許多模擬和原型設計系統的基礎裝置。

ASIC模擬和原型設計系統支援許多與IC和系統開發相關的工作,包括使用真實硬體的演算法開發、晶片製造前的早期SoC軟體開發、RTOS驗證、針對硬體和軟體的邊角案例條件測試(corner-case condition testing)與連續設計反覆運算的回歸測試(regression testing)。

模擬和原型設計系統旨在幫助半導體廠商在晶片製造前發現和避免代價高昂的軟硬體設計缺陷,從而節省數百萬美元的成本。原因是晶片在製造完成後,解決硬體設計缺陷問題成本更高,通常需要昂貴的重新設計費用。當製造出來並交付給終端客戶後,解決這些問題的成本會更高。因此模擬和原型設計系統的使用越來越普及,因為在經濟成本如此之高的情況下,沒有哪個設計團隊負責人會忽視這項謹慎的驗證性投資。

更重要的是,用來製造Intel Stratix 10 GX 10M FPGA的半導體和封裝技術,不僅是為了製造最大容量FPGA,最大的重點在於這些技術讓英特爾能夠透過整合不同的半導體晶片,包括FPGA、ASIC、eASIC結構化ASIC、I/O單元、3D堆疊記憶體單元和光子器件等,來將幾乎任何類型的裝置整合到封裝系統(SiP)中,滿足特定客戶需求。這些先進技術彼此相輔相成,構成了英特爾獨特創新並且極具策略性的優勢。