AMP、Grid-on-Chip、SMP等多核心設計

- DIGITIMES企劃

嵌入式產品設計,最大的優勢就是可採行最精簡的硬體系統來完成指定的功能需求項目,達到操作最簡潔、同時兼具低成本與高效能的應用基礎,而當嵌入式產品設計被賦予的功能越來越多後,現有的SoC解決方案也開始朝多核心設計架構發展,在原有設計方案下,提供更高的處理效能與系統反應效率...

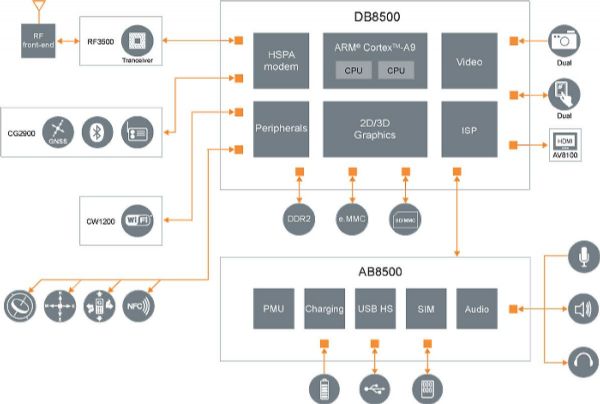

利用SoC(System On Chip)的手段,把多處理器甚至是以往採離散式設計型態的圖形處理、音效晶片、DSP(Digital signal processing)、視訊編?解碼器等,一一整合成一個單片型態的處理核心,利用這種開發手段,SoC不只較同等的單核心設計方案更為精省,且多核方案可以有效將運算負荷透過各專用核心紓解運算可能產生的瓶頸,同時主運算核心也不用一昧地利用拉高系統外頻來增加效能,而是可用SMP對稱核心的分工運算,達到相同或少許提升時脈下即可獲得倍增的運算效能。

以單一SoC設計或是局部SoC來進行功能整合,是嵌入式應用領域相當常見的設計方案選項,利用整合晶片的高度晶片內連接與整合,可讓原先具固定佔位面積的料件可以因為晶片內的功能核心整合,讓數個晶片微縮至僅需一個晶片就能完成,一方面減少零組件數量,同時也能降低系統的料件成本與強化系統的功耗表現。

但要讓採多核設計方案的硬體架構充分發揮效能,除硬體在晶片、電路載板布局各方面進行工程段的開發努力外,基本上仍須加入軟體團隊,針對多核架構的硬體現況,來將系統軟體做最有效的多核性能調校整合,僅有系統與硬體的多核最佳化搭配,才能讓嵌入式系統可以在低功耗、高度簡潔的架構設計下,維持近似或更低的耗能,同時可處理的資料量、系統反應效能卻能因為多核架構而同步提升。

多核心整合架構 應強調單一核心最佳化運行

雖然現有嵌入式SoC趨勢是往多核心方向發展,但實際上在進行應用核心的多核設計之前,仍必須針對多核心設計進行應用劃分設計準備,尤其是要針對重要架構的細節進行深入檢查。

例如,網路路由器的嵌入式設計方案,在Level-2 router或Level-3 router產品,多數的產品設計方案都若朝為傳統路由器架構更多管理功能、或應用方案,讓原產品可以擴充如Level-4以上的路由器應用方案,來達到產品差異化設計的目標。若是單核心設計方案,為提升追加功能性的執行效能,通常只能利用提高外部時脈進行性能提升,但單核心方案在性能提升方面可能會因物理限制而無法無限制的提高,勢必要尋求多核設計方案來改善產品表現。

現有的多核心元件,工作外頻可以在800MHz~2GHz不等,核心的數量可以從多核心的最低量雙核一直到8~16核心不等,但想利用多核設計來強化整體運算效能,仍必須考量系統底層的支援特性,在一般設計中單核心方案強化效能可從增加快取或是提升外頻來衝高效能表現,而多核設計方案除了利用多核心的硬體優勢外,如何讓多核心各個單一核心可以在最佳化的狀態運行,就考驗著分配運算任務的處理效率。

多核心設計方案 並非核心數越多效能就能翻倍

AMP(Asymmetric multiprocessing)或稱為ASMP的設計方案,會把運算任務分成兩大部分,一部分是控制相關任務,而另一部分為數據相關任務。像是數據相關的任務如使用DSP來進行,而利用一組通用CPU來進行系統的正常運行,這種設計方案可讓系統與除錯工具都相對單純。

在嵌入式設計方案反而較常應用對稱式(Symmetric Multiprocessing;SMP)多核心設計方案來實現,即使SMP的運算管理相對較AMP單純許多,但實際上不管是AMP還是SMP設計方案,當核心數量超過2個以上後,運算性能的提高效益就不可能呈核心倍數增長,因為寶貴的CPU運算週期會部分用於多核心處理器的運算任務協調,致使整體的SoC運算效率提高的效益受到限制。而因多核硬體整合所提升的效能,並非核心越多、效能就能得到對應的倍數提升,反而必須視如何維持高效率的工作分派運算與協同處理,才能得到接近的提升效益。

Grid-on-Chip多核設計方案

Grid-on-Chip即晶片上柵格(或簡稱「柵格」)模式,為由許多完整獨立之與網路互連的運算節點所組成的多處理器系統。在Grid-on-Chip中每個晶片共享相鄰實體鏈路,但每個運算單元仍維持獨立的網路處理節點。

Grid-on-Chip也可以說是分散式多處理系統,可以算是AMP、ASMP的設計方案之一。應用Grid-on-Chip首先要分割系統、尋找合適的節點進行通訊,即便是高階的Grid-on-Chip系統可在執行過程自行重新配置資源,但開發時仍須針對Grid-on-Chip思考系統功能與每個運算節點的系統分配問題。

除分割問題外,Grid-on-Chip系統其實在設計限制算是最少的,即便系統遭功能分割,每組運算節點的設計基礎仍等同獨立的子系統運行,Grid-on-Chip模式系統與其他設計的優點是,Grid-on-Chip可以很容易地與軟體進行整合,系統也能在單一柵格範圍內完成應有的計算任務,此外,Grid-on-Chip系統設計方案在除錯工作亦相對簡單不少。

至於「分割」,是Grid-on-Chip的主要優勢,但實際上也是分割的系統讓Grid-on-Chip的缺點特別凸顯,因為系統的分割讓架構難以再分配資源,尤其Grid-on-Chip在面對不可預期的計算要求時,系統的靈活性就會較低。

SMP的多核心設計方案

至於目前最普遍的設計方案,就屬對稱多處理器架構(SMP)莫屬,此為single-image作業系統執行在2或數個共享處理核心、存儲空間的設計方案,而這些核心處理器在各自的核心架構上大多為一致設計,在SMP模式架構下,系統可在如同一個處理器核心的基礎上進行動態分配運算工作。

尤其在可快速重新分派處理任務的能力方面,是SMP系統架構的優勢,這也是SMP系統較AMP/ASMP或是Grid-on-Chip等多核心方案中最具使用靈活性與系統適應性的設計方案,運行於SMP的即時作業系統的架構靈活度,可在不犧牲性能的條件進行任務分派與即時回應系統需求。

每個SMP架構都必須具備兩個要件,一是對稱之共享記憶體的多核心處理平台,另一個是必須支援SMP架構設計的作業系統,現今不只是Android嵌入式系統,多數嵌入式應用平台已支援了SMP架構應用,同時作業系統的選擇也較以往多元,開發人員可以快速導入較熟悉的系統平台,在最有效率的時程完成SMP嵌入式應用開發,不管是移植舊有的應用設計方案,或是重新架構新的硬體架構,SMP架構方案可輕鬆、快速地運用多核心硬體優勢來提升整體運行效能。

但整合SMP應用時仍須注意一些問題,例如,若嵌入式設計需要考量即時反應需求,搭配支援SMP的即時作業系統(Real-Time Operating Systems;RTOS)雖然不會影響即時反應效能,但使用SMP即會因為系統整合,導致系統缺少更高階與可變中斷的反應時間,這在慣用單處理器的RTOS系統產品上可能會與採多核心設計的產品表現略有差異。

此外,SMP應用於嵌入式系統的另一個問題,在於系統資源的競爭設計,雖然SMP的優點是硬體資源共享設計,這同時會讓嵌入式SMP系統具系統靈活度與更高的適應性,但這個優點同時也是個缺點!因為資源共享的關係,也讓SMP的系統資源競爭會出現較難因應且無法預期的性能變化,開發人員在架構應用時需同時考量應用的設計架構。

- 高解析度發燒 行動裝置多核GPU應用成趨勢

- AMP、Grid-on-Chip、SMP等多核心設計

- Smart TV、STB帶動嵌入式處理器朝多核心架構重點升級

- Sophia System推出ARM 4G ETM高速追蹤除錯器

- ARM與台積公司攜手共創64位元處理器最佳化

- iPPea TV支援Android系統數位電視外接器

- Intel Xeon E5系列 獲Top500超級電腦愛用

- 向日葵5.0攜手高通創銳訊佈局遠程控制一體化

- Intel Core處理器提供更驚艷的行動運算體驗

- Silicon Labs新無線IC簡化嵌入式設計與效能

- Android NDK應用程式將可支援MIPS架構

- 2012高通Uplinq大會演示行動技術平台生態