發揮最大電池驅動效能的行動多媒體裝置系統設計

- DIGITIMES企劃

行動多媒體裝置持續推陳出新,不管是PMP行動多媒體播放器、平板電腦,甚至更多元化的媒體應用裝置,都朝向功能不斷整合的方向發展,在功能方面追加了無線通訊、網路支援,性能方面持續強化核心處理器的運行效能,但這些改變趨勢壓縮了裝置的電源使用效率,改善系統的電源使用效能除了加大電池容量之外,還有哪些選擇?

行動多媒體裝置持續朝小型化發展,這造成內部PCB的可用空間持續壓縮,在相對嚴苛的設計條件下,系統開發者若僅採取以參考設計為基礎進行功能開發,可能在節電、效能、體積等多方面都會影響到終端裝置的性能表現。

尤其,Apple推出iPad與iPad 2之後,大力推銷其產品具備超過10小時連續使用的電池性能,讓一般消費者對於行動裝置的電池效能要求變得更為嚴苛,從以往的連續使用3~4小時,一舉提升到至少要連續可用8~10小時之譜。電池效能要求持續增加,系統端的設計也不能一昧地朝加大電池容量方向進行設計,反而必須在更多設計層面強化電池的電源管理,以達到延續產品電池使用效能的設計目的。

針對能源耗用關鍵元件 選用相對節能、高效能解決方案

觀察行動多媒體裝置,耗用較多系統能源的元件,應為屏幕驅動、屏幕背光驅動、核心處理器、記憶體存取、無線網路存取、電源控制電路...等元件,尤其是屏幕、屏幕背光、核心處理器應是佔系統能源較多者,在考量如何提升電池供電效能的設計方針時,必須先解決屏幕、屏幕背光與核心處理器的關鍵元件選擇。

在屏幕方面,目前有多樣化的選擇,像是LCD、AMOLED、IPS LCD等,針對解析度與反應速度的不同,又有元件方面的功耗差異,但除了AMOLED目前不需要背光設計外,採取LCD基礎的IPS與基本型LCD均需要背光設計。

目前顯示屏幕持續朝高解析度方向發展,以熱門的iPhone 4為例,其Retine顯示屏幕可在3.5吋面積具備960 x 640的顯示解析度(326ppi),在多數應用設計中,顯示屏幕還須整合多點觸控設計,在種種的功能追加與性能追加方面,讓顯示面板的驅動功耗不能只觀察顯示所需的功耗需求。在節能的設計考量上,顯示屏幕基本的運作功耗,討論相對較成熟的LCD或IPS LCD顯示屏幕,在功耗的降低方面可能相對較無空間,在元件部分已經決定了整體使用的功耗基礎,但在觸控功能的部分,則可選用相對較低的解決方案,或是在小屏幕的應用方案中,不需導入多點觸控設計,藉此壓低整個螢幕模組的驅動功耗需求。

除元件方面的省電性能考量,其實在系統端的驅動控制設計,也可朝向更細緻的面板控制設計進行相關功能開發,例如,產品系統若類似數位相機、行動電話等產品時,可在裝置上設置近接感應器,以相機應用為例,當使用者取相機透過觀景窗進行拍攝、構圖時,由於臉部湊向相機機身,此時LCD的顯示內容已無必要性,若系統整合時考量透過近接感應器去關閉LCD顯示功能,即可在不同應用模式下減少不必要的功耗發生。此狀況也可用於行動電話設計,整合近接感應器在接聽電話時關閉屏幕顯示,亦可達到相同的節能效果。

同樣的,在顯示屏幕的背光設計中,目前幾乎8成的行動裝置都改用更省電的LED背光光源,但LED的省電效能有限,必須透過更多設計方法去進行改善,例如,若是中、小屏幕設計裝置,背光的設計就可改成上/下或是左/右側光型背光,減少LED光源元件的數量,達到減少功耗的設計目的。除此之外,先前針對LCD驅動搭配的近接感應器,也可與LED背光光源驅動控制進行整合,讓近接狀態時可以適時關閉LED背光光源,這可讓使用者的操作體驗更好,同時又可達到省電目的。

另外,在背光源的功耗節約設計方面,系統設計者亦可善用光感應器來搭配節能設計,例如,在行動裝置的面板正面邊緣設置光感應器,藉此測得用戶使用環境的照明水準,若是亮度較高(強光下或戶外),即強化背光驅動功率去改善顯示效果,若處於一般室內或是低光源環境,也可同步調低螢幕背光,達到節約整體裝置功耗的目的。

目前多數行動裝置,如智慧型行動電話、平板電腦...等,幾乎全面採用相對省電的ARM處理器,而目前ARM系列核心處理器運作時脈也有1G~1.2GHz解決方案推出,但實際上提升核心處理器的效能並非只有持續拉高時脈才辦得到,因為單一核心元件若時脈持續增加,元件本身功耗可能相對增加,但效能卻無法有效提升,甚至還會增加處理元件散熱的額外成本。

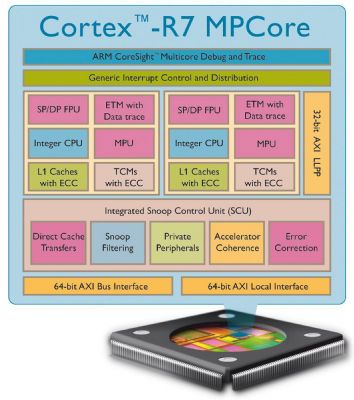

以現有的解決方案觀察,核心處理器也與桌上型電腦的處理器趨勢一樣,採取以單顆元件、多個核心的設計方式,去改善單處理器的效能瓶頸,例如,Apple的iPad 2新產品就採取新版A5處理器,利用A5單一封裝裝載2組ARM核心的設計方式,達到效能較前代產品倍增、多媒體呈現較前代效能有9倍提升的效益。而在採取單元件、多核新設計前提下,其實整體增加的功耗並不多,反而還可以得到效能提升的助益。

無線RF相關模組的省電設計方針

綜觀行動裝置的應用方式,除了處理核心運算應用的微處理器為耗能角色外,若不考量顯示屏幕的尺寸所需驅動面板與背光耗能,其實最大的耗能來源應該屬於無線、RF射頻傳輸造成的能源消耗。

以目前使用的主流技術為例,無線應用的部分有行動通訊(CDMA、3G/3.5G/WiMAX)、近距離無線通訊(藍牙、Wi-Fi)為主,以行動通訊應用來說,因為相關資料必須透過長距離的基地台交互傳輸資料,在無線模組的功耗較難進一步壓縮,但以免許可的2.4GHz頻段的Wi-Fi、Bluetooth更應善用其節能的設計功能,而這也是目前在行動裝置使用量最高的中、近端網路應用,對於裝置的電池耗用佔一定的程度比例,系統設計若未能將其深入考量,可能會影響整體的電源使用效率。

例如,以藍牙無線傳輸(bluetooth)4.0技術為例,在一般應用中,藍牙的規格可支援裝置10m周邊內的低速傳輸應用需求,主要是著眼於藍牙的傳輸技術,在於低成本、短距離、可互通作業特性,藍牙無線傳輸技術一開始在規格制定與功能開發,就以極低功耗(ULP)為開發目的,因為藍牙主要用來取代如USB或低速周邊的傳輸無線化的目的設計,若無ULP應用思維,可能就成為系統電源耗用的元兇。

而藍牙無線應用設計,實際上應在因應不同裝置連線要求上,進行更精細的設計。例如,當藍牙用於無線耳機連接應用時,實務的應用可在維持基本連線(無通話)狀態時,採取可變連接時間間隔方式,去取得裝置持續連接的回應狀態;若當藍牙耳機處於通話狀態時,則轉換為較高傳輸率的應用模式,維持最佳無線通話品質。

這種應用模式也可用於如滑鼠或其餘無線周邊,在大量應用時透過BLE(Bluetooth Low Energy stack)技術快速連接,平時裝置處於連接但未使用時,僅以鏈路端點告知雙方正在連接範圍,隨時可以提供連接服務狀態,而實際維持裝置連接狀態確認傳送的設備數據,應儘可能減少數據量,同時減少發送次數,以達到節省通訊消耗的功耗為目的。

有效降低待機所需電源 朝極低待機功耗目標努力

若以行動裝置的使用慣性觀察,一般裝置全時工作時間會有2/3或更多是處於待機狀態,但在現行裝置要求的立即開啟、立即使用的應用模式中,讓裝置系統必須因應此需求,為裝置的核心晶片或暫存系統、暫存器、晶片目前待機組態等資訊提供最小的維持電力,以在下次開啟時讓系統快速恢復裝置關閉前的操作狀態。

一般的思考方式是認為,待機所使用的能源消耗極小,但實際上待機的電源耗用卻並非如此!因為多數的電子系統設計,在待機或無負載的狀態下,其維持待機的電源消耗仍相當驚人,甚至部分低劣設計的山寨產品,根本就不在乎待機設計,所謂的「待機」模式僅是將LCD屏幕背光關閉,卻讓核心處理器、系統電路維持在原有全速運行的使用狀態,造成開機與待機的電源功耗相當,大幅縮短行動裝置的能源使用效率。

尤其是採行電池供電的產品設計,對於待機的要求應該在設計層面投入更多開發資源,例如,必須在產品開發初期即確認裝置的不同使用狀態對電源耗用的量表,例如,在正常、高速、低速、待機、睡眠、深層睡眠等狀態模式下,設定明確的系統功耗指標,讓電源電路、主控電路、邏輯電路、周邊介面等設計區塊,都能盡力呼應到整體的電源管理設計目標,讓整體電子電路設計均能依循降低功耗的設計方針進行系統開發。

目前多數的電子裝置,例如目前最熱門的Android平板電腦,開發廠商大多習慣採用系統晶片業者提供的參考設計再進行相關電路布線改善,較用心的開發者會思考強化節能的附加功能或設計,稍不用心的設計者沿用既有布線設計,而忽略整體的能耗控制設計,造成產品良莠不齊。

在待機模式的能耗降低設計中,若要保有最佳系統反應時間,必須在著手設計前先確認系統關鍵晶片的待機前資料保存需求,歸納出必須即時保存與將資料取回的轉換時間,並針對核心晶片確認其待機條件是否能滿足設計,而待機的能耗問題通常在核心處理器問題較少,因為核心處理器通常都會有多種標準運行模式設計,待機模式也會分幾種程度性的差異,系統開發時需要重新開發或是調整的空間較少。

反而是周邊的功能模組、匯流排、系統晶片的待機方式,多為系統開發工程師來定義,若沒有明確定義並進行相關設計要求,就可能出現有時自待機恢復時,卻出現顯示錯亂、觸控不靈光,甚至資料回存失誤等問題。

一般無硬碟的行動裝置,要自待機模式中喚醒,多數必須要求在1,000ms以下,若超過數秒才能喚醒系統,則已失去產品的實用性,尤其在平板電腦、智慧型手機這類裝置中,特別是手機部分,更需要縮短待機喚醒時間,至少要求在500ms內恢復顯示與可供用戶進行操作的狀態,至於如何達到縮短待機喚醒時間的要求,就必須在省電與提高反應速度之間進行權衡設計。

電源電路面臨可用空間持續縮小的因應設計

在電子設備的體積持續縮小的趨勢下,今日的電源系統開發工程師面對產品不斷縮小、應用功能持續增加的挑戰,這一方面也意味著電源電路可以分到的PCB主板空間越來越小,此方面的問題將會產生系統的功耗、熱處理問題與整體線路布局的影響。

電源工程師在應對這類設計問題,大多只能透過元件方面的技術升級,進行電源電路縮小與效能提升設計,像是常用的電源IC為採MOSFET技術,搭配新式封裝設計,但新的應用需求卻必須採取更小的空間去乘載這些關鍵元件,而不只是單單主板面積需要減小,連元件本身的高度,也必須大幅壓縮,才能因應新的產品設計要求。

現在的電源IC設計封裝,已從SO-8標準接腳封裝的設計模式,逐漸進行調整,目前多數設計會採取底側引腳或底側焊盤的功率封裝設計,而針對高電流應用部分,在一般性的設計方案中多採取PowerPAK的SO-8以5mm x 6mm方式封裝,在低電流的主板設計應用方面,新的設計方式為採取PowerPAK 1212-8封裝(3mm x 3mm),這類封裝的RDS(on)表現佳,尤其在行動裝置(如筆記型電腦)採10~15A的DC-DC應用類型,PowerPAK 1212-8封裝是相當常見的解決方案。

雖然多數的應用設計中,3mm x 3mm的PowerPAK 1212-8封裝似乎已經可以因應多樣的設計需求,尤其是產品體積縮小化的開發需求,但實際上還有進一步縮小空間需求的可能性。在DC-DC電路應用中,若要採取更小的設計空間,多數可用雙元件封裝來替代分離式設計的MOSFET元件,尤其是因應小於5A的負載設計方面,採取Dual SO-8 MOSFET因應小電力的DC-DC綽綽有餘,也可縮小元件的佔位面積,尤其是當主板的DC-DC應用多為5V、3.3V時,此種元件選用與設計方式更具優勢。

而雙片式的設計,尤其是在MOSSFET元件方面,選用雙片功率封裝具有許多好處,因為這類封裝方式可以達到較佳的熱性能,與取得最大的元件輸出電流,原本雙晶片的佔位空間與元件間的布線都相對造成空間佔用,但採雙晶片功率封裝可以讓元件具雙晶片優勢,同時僅需單晶片的佔位空間,等於是簡化更多設計同時縮小產品體積,輕鬆改善元件的佔位狀態。

電源設計工程師除可善用不同封裝特性的電源處理IC,也可在不損及電源安全與維持最佳化電源使用效率的要求下,將DC-DC轉換電路的設計儘可能簡化、縮小,節省PCB主板空間,甚至可搭載更多主動或被動省電機制,讓整體行動裝置的電源應用達到最佳化的境界。

- 觀察iPad 2縮小體積、維持產品用電時效的設計關鍵

- 發揮最大電池驅動效能的行動多媒體裝置系統設計

- 奧地利微電子推出具有喚醒及省電功能的全新10位元磁旋轉編碼器

- 英飛凌推動高效率電源轉換設計 中電壓MOSFET讓CanPAK產品系列更臻完備

- 安茂微發表AME5280 DC-DC高效能電源管理控制器

- 持續為終端產品提供高效率及低功耗解決方案 安茂微電子期望成為高附加價值之電源管理IC領導者

- IR收購CHiL Semiconductor 加速開拓高速增長的數位功率市場

- 漫談節能LCD電視的LED背光區域調光

- Cirrus Logic推出效能及價格均優於類比PFC的數位功率因素校正IC-CS1500及CS1600

- 恩智浦半導體推出業界首款10Gbps CMOS多工器/分工器開關 CBTL02043支援高頻寬系統 同時達成最低功耗

- 恩智浦半導體以全球最低待機功耗技術引領潮流 高效GreenChip系列低功耗配接器可同時節省成本與能耗