提升視訊處理效能 SoC整合顯示記憶體多元架構

為了提高使用者體驗,原有針對節省料件成本、簡化物料清單項目而開發的SoC元件,也逐漸需朝向提升運作效能、整合高效顯示晶片,甚至內嵌顯示記憶體以強化產品表現,同時,也是基於壓縮成本考量,SoC的嵌入顯示設計方案,也必須兼顧成本與效能考量...

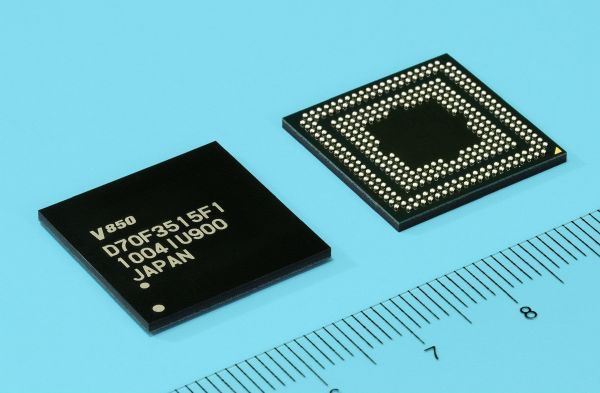

SoC(System on a chip)系統單晶片技術方案,隨著應用潮流變遷,原有基於縮小產品體積、縮減料件成本目的,在消費者越來越要求產品效能表現下,SoC也被賦予更高的效能要求。例如,直接影響用戶操控體驗的視覺相關圖形處理設計,就成為首要強化整合方案的關鍵表現。同時,SoC技術方案也被賦予高度整合系統的高標準要求,原先採外部設計方案的設計應用項目,也逐一被納入SoC整合方案之中。

SoC嵌入式應用 內嵌顯示應用系統負荷持續增加

對於嵌入式顯示的SoC應用方案,可以說是多數SoC產品首要整合的重點項目,早期大多僅提供基本嵌入式顯示支援功能方案即可,但新的應用領域,對於高度3D應用內容已逐漸顯得吃重,必須導入具3D重繪加速的高階應用功能,相關應用環境也越來越嚴苛。

至於解決新應用的方法,必須在SoC產品中導入創新之複合記憶體架構,利用可整合於系統的控制器和快閃記憶體元件,同時減低使用外部隨機存取記憶體的機率,進而透過資料存取均在SoC內部連結元件內的絕對優勢,而達到加快圖形畫面重繪、3D物件處理與顯示速度大幅提升之效用,令嵌入式顯示的實際展演效能,可以達到接近桌上型電腦或筆記型電腦的應用水準。

因應3D圖形重繪需求 顯示記憶體數量持續增加

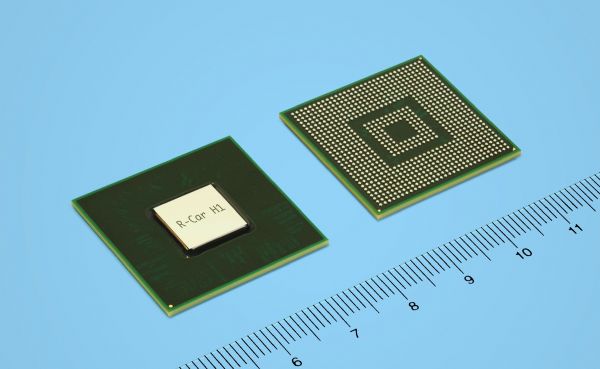

在多數嵌入式系統中,多少都會有設置顯示器的需求,而建構系統所採行的系統單晶片(SoC)產品,當用於汽車、醫療、遊戲或是家用電視連接應用時,這類SoC平台就必須搭配高容量之記憶體,來支應持續暴增的數位內容呈現需求,尤其是針對3D即時貼圖呈現的3D場景建模畫面,對於圖形顯示所需的顯示記憶體容量往往會高於4Gb以上。

在嵌入式系統常用架構中,通常會採行搭配數位視框緩衝器(Frame Buffer)來搭配產出輸出影像,由SoC內嵌之顯示控制器,透過視框緩衝器在顯示器上形成一禎禎的視框畫面。

SoC與內部圖形加速引擎,透過整合內部(或外部)視訊記憶體途徑,獲得處理儲存視框緩衝器內的場景視訊、角色貼圖,供重建顯示畫面之用,SoC則經由高頻寬介面I/O取得儲存於外部儲存設備之資料,完成整個視訊處理與輸出程序。觀察其運作過程即會發現,影響SoC嵌入式系統整合晶片處理視訊的運行關鍵,即是大量的視訊處理與操作均得經過高速I/O進行資料存取,但實際上外部I/O的效能提升相當有限。

為滿足低成本要求 需在有限資源內榨取最高效能

加上嵌入式系統多要求採低成本建置,對於PCB載板的設計方案相關資源較少,無法採行較佳的設計方案,若為求加速SoC視訊處理性能而過度依賴高速外部I/O,這會造成設計方案成本提高,不只是I/O線路的增加,外部記憶體料件的佔位空間也會對整體設計造成影響。

在導入高性能圖形處理架構的嵌入式設計方案中,常見採行標準型Code-shadowing記憶體架構,一般由系統核心處理器與通用處理器之高度整合,包含圖形處理引擎、顯示控制器,搭配有限的嵌入式隨機存取記憶體(RAM)與儲放系統應用程式碼之快閃記憶體(Flash Memory)...等整合項目,而SoC本身同時仍可搭配外部記憶體介面進行擴充。

至於外部記憶體部分,則分為動態隨機存取記憶體(Dynamic Random Access Memory;DRAM)與快閃記憶體兩種料件,而一般嵌入式系統啟動後,會先自快閃記憶體提取程式碼,取得程式碼後轉至DRAM較高速環境進行執行程式碼之映射,同時搭配處理器、DRAM、關鍵元件的系統初始化程序、應用程式開啟運行後,程式即自動進行工作。

若是在此種SoC應用架構下運行,必須搭配SoC DRAM整合之高速存取技術方案,提高處理畫面重繪之效能,透過強化此傳輸架構之性能表現,縮短系統初始化所耗用的時間,同時加速Flash Memory的存取I/O頻寬,進而達到系統運行提速同時轉送與處理顯示資料的效能提升目的。

針對NOR/NAND快閃記憶體差異 需在應用架構中調整設計因應

但SoC中快閃記憶體的存取頻寬、快閃記憶體與系統至DRAM之間的傳輸資料密度,設計方案已經限制了映射時間的效能表現。目前Flash Memory已有多種非揮發性記憶體的技術方案因應嵌入式產品需求,常用的Flash Memory技術方案為NOR與NAND兩種快閃記憶體方案。NOR與NAND兩種快閃記憶體的技術架構不同,進而影響了SoC嵌入式系統的資料存取性能、系統可靠性、產品使用壽命,同時不同的快閃記憶體方案其單位料件成本架構亦不相同。

至於現有SoC產品,為了讓開發端便於整合應用方案之用,所使用的SoC架構方案也通常同時支援多種記憶體I/O介面組合,以便因應串列?並列設置之NOR快閃記憶體、或支援高容量之NAND快閃記憶體介面產品。

加上快閃記憶體設計方案正持續不斷創新,這同時也產生了更多具成本效益的複合型數位顯示架構可供開發產品選擇,利用系統控制器與不同架構之快閃記憶體搭配組合,已開發整合型態之嵌入式顯示效能提升方案,在資源有限的嵌入式系統SoC應用環境中,開發更具經濟效益、容易架構之SoC單晶片顯示解決方案。

系統控制器可執行來自SoC內的嵌入式快閃記憶體中預儲的程式碼資料,又能透過高頻寬多I/O串列之SPI周邊介面,可讓SoC得以從外部快閃記憶體進行圖形資料加載程序,至於圖形資料可經過處理後再轉送至內部視框緩衝器裡後,同時顯示於SoC接續之顯示屏上。這類採複合型架構的設計方案,同時可滿足系統的高效能要求與整體設計方案的高可靠度設計要求,加上設計方案不用搭配外部圖像處理記憶體,也可藉此減少使用料件清單的DRAM料件項目,進而降低系統設計成本。

但使用上述設計方案應注意複合型架構與快閃記憶體整合型態,可能會讓快閃記憶體承受大量的讀取次數,這對於使用NAND型快閃記憶體的架構產生壽命上的衍生開發議題,因為NAND型快閃記憶體會有料件的讀寫壽命問題,再加上已高頻率進行大量、頻繁的NAND讀寫動作,也會因為NAND本身的料件物理特性,出現記錄位元彼此干擾的狀況發生,若採行此種系統設計方案,必須嚴密測試產品可能產生的設計問題。

- 提升電子設備節能效率 數位化電源設計突飛猛進

- 從元件、驅動電路設計 改善LED照明應用效益

- 提升視訊處理效能 SoC整合顯示記憶體多元架構

- FPGA SoC化應用架構 導入多核心CPU支援

- 功得電子參加台北國際電子展 發表突破性產品

- 通訊教育的最佳選擇 固緯3GHz頻譜分析儀

- 電子展鑫創展出全球最小CMOS微機電麥克風

- 致茂能源回收式電池模組測試系統獲科技創新獎

- SCHURTER TA35熱斷路器獲ISO 22196認證

- Maxim D類數位揚聲器放大器有效簡化設計

- ROHM推出支援13芯低耗電鋰電池保護IC

- 實現更小更低成本的監控鏡頭

- 電子展儒毅科技將展出AptBee雲端服務系統

- 電子展、寬頻通訊展與雲端暨物聯網展

- 功得電子推出UDE系列500VAC/DC保險絲

- 電子3展 非參加不可的3大活動

- 2012電子三展開拓智慧、創新與綠色商機