GUC UCIe 64G IP在台積電N3P上完成設計定案

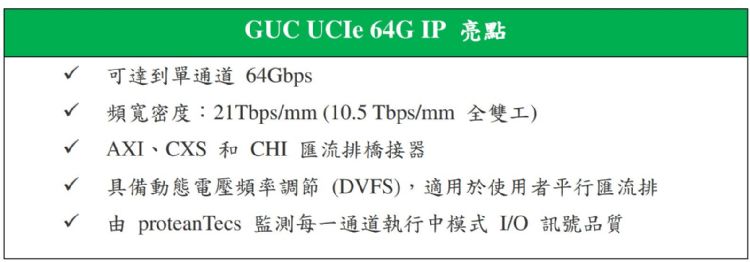

先進特殊應用積體電路 (ASIC)領導廠商創意電子(GUC)近日宣布成功推出業界領先Universal Chiplet InterconnectExpress (UCIe)實體層晶片,實現UCIe規格定義中每通道64Gbps的最高速度。

創意電子的UCIe 64G IP支援UCIe 3.0,能提供每1公釐晶粒邊緣21Tbps(10.5 Tbps/mm全雙工)的驚人頻寬密度。創意電子藉助於台積電的先進N3P技術和CoWoS先進封裝來達成此一里程碑,旨在鎖定AI、高效能運算(HPC)、資料中心和網路等應用領域。

為了方便整合,GUC利用UCIe串流通訊協定,開發了適用於AXI、CXS和CHI匯流排的橋接器。這些橋接器經過最佳化,具備高流量密度、低延遲和低功率的特色,搭配高效率的端對端流量控制,促進從單晶片 NoC架構到小晶片系統的無縫轉變。它們支援動態電壓頻率調節(DVFS),實現數位供應電壓和匯流排頻率的即時變化,同時確保資料流不會中斷。

創意電子的UCIe IP也備有多項進階可靠性功能,包括UCIe Preventive Monitoring(預防性監控)功能,以及由proteanTecs提供的整合式I/O訊號品質監控功能。

這項技術可在無需重新訓練或中斷操作的情況下,對資料傳輸期間的訊號完整性進行不間斷的任務模式監控,不僅可獨立監控每個訊號通道,還能即時偵測功耗和訊號完整性異常。如此即可及早辨識凸塊和傳輸線缺陷,藉此觸發修復演算法,以透過備援I/O取代接近臨界點的I/O,從而防止系統故障。此一主動積極的方式可大幅延長晶片的使用壽命,並強化系統可靠性。

創意電子技術長Igor Elkanovich表示:「基於台積電先進的製程與封裝技術,我們致力推出效能最高、功耗最低的2.5D/3D小晶片及HBM介面IP。2.5D與3D封裝技術現在都趨向使用HBM3E/4/4E、UCIe-A和UCIe-3D介面,有助於開發出超越光罩尺寸限制的高度模組化處理器,進而為新一代的高效能運算鋪路。我們與台積電及其開放創新平台(OIP)生態系統的緊密合作,使我們的客戶能夠在當今人工智慧驅動的競爭市場中加快產品上市速度」